Writing to NIC at IO3-7 always writes a 9F. Read works fine.

Posted: Fri Apr 19, 2024 3:23 am

Hello everyone,

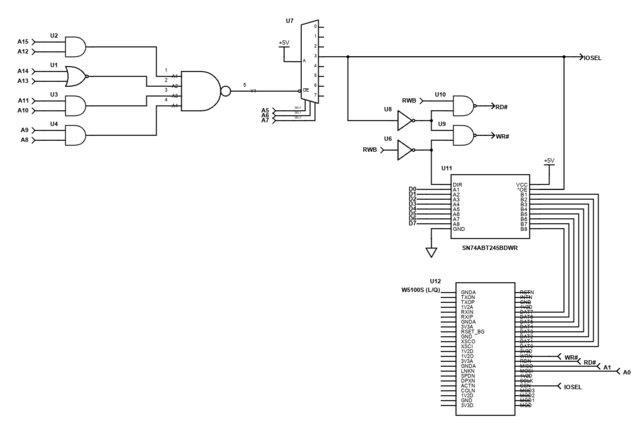

I've been working on a 10/100 NIC for a few weeks now and I almost have it working. For some reason though when I try to write to the card at IO3 ($9f61) or any other IO address, it always writes a $9f to the device. The chip that I am using for the ethernet controller is the Wiznet W5100S. Looking at the timing diagrams of the W5100S and the 65C02 everything appears to be OK even at 8MHz. While I was fairly confident that I was meeting timing requirements I still even tried ANDing the CS with the clock but still the same results; reads just fine but always writes a 9f. I feel like I'm missing something here, which is very possible as I'm fairly new to 65C02 assembly and building hardware for it. I can provide a schematic of the IO select and R/W logic if need be.

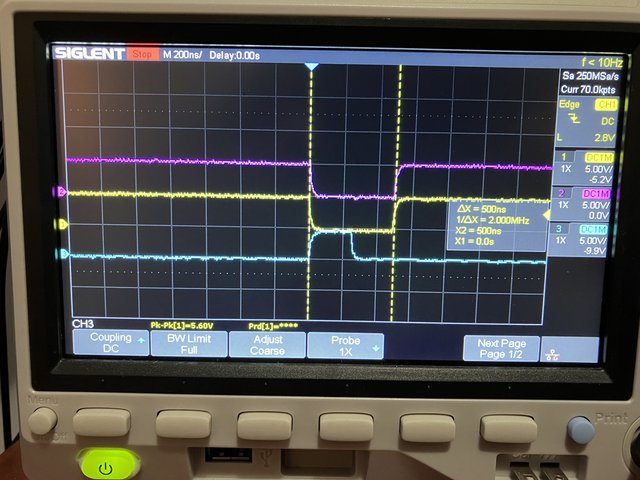

The picture below shows the CS (Yellow) WR# (Pink) and D0 (Blue). As you can see, bit 0 is set when the CS and WR signals go low ($9f).

Apologies if this is a newb mistake. Any help would be most appreciated.

Thank you.

I've been working on a 10/100 NIC for a few weeks now and I almost have it working. For some reason though when I try to write to the card at IO3 ($9f61) or any other IO address, it always writes a $9f to the device. The chip that I am using for the ethernet controller is the Wiznet W5100S. Looking at the timing diagrams of the W5100S and the 65C02 everything appears to be OK even at 8MHz. While I was fairly confident that I was meeting timing requirements I still even tried ANDing the CS with the clock but still the same results; reads just fine but always writes a 9f. I feel like I'm missing something here, which is very possible as I'm fairly new to 65C02 assembly and building hardware for it. I can provide a schematic of the IO select and R/W logic if need be.

The picture below shows the CS (Yellow) WR# (Pink) and D0 (Blue). As you can see, bit 0 is set when the CS and WR signals go low ($9f).

Apologies if this is a newb mistake. Any help would be most appreciated.

Thank you.